Mémoire et logique non-volatiles embarquées basées sur des circuits ferroélectriques – Newsletter 5

https://www.youtube.com/watch?v=M8tL-nN7G-A

Le projet européen 3eFERRO introduit un nouveau matériau ferroélectrique (Hf(Zr)O2) pour créer des cellules de mémoires FeRAM compétitives dans le contexte de l’Internet des Objets. Ce projet vise également l’exploration des concepts de calcul en mémoire non-volatile basés sur des cellules FeRAM et FeFET.

Il regroupe 8 partenaires parmi lesquels: le CEA, ST Microelectronics, Namlab (leader dans le domaine des circuits ferroélectriques HfO2) ainsi que 5 grand laboratoires de technologies. L’ensemble de ce consortium est originaire de 5 pays différents de l’UE.

Dans le numéro 5 de la newsletter, les 3 parties de ce projets sont mises en avant sont:

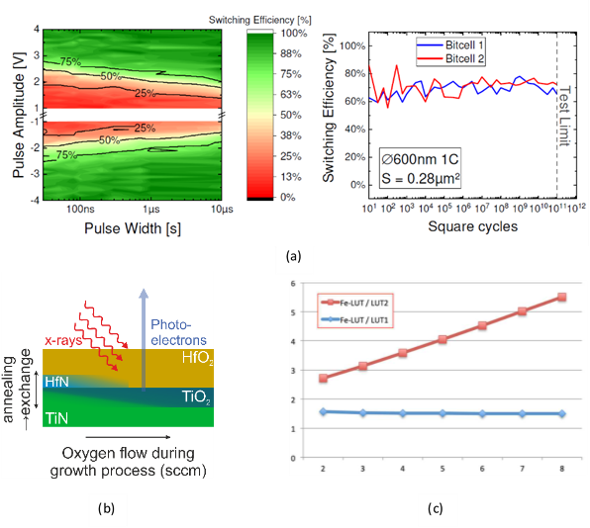

- Le travail effectué sur l’interface HfZrO2/électrode

- L’intégration des condensateurs ferroélectrique

- les circuits logique a base de FeRAM et de FeFET.

Dans le numéro 4 de la newsletter, les 3 parties de ce projets sont mises en avant sont:

- L’exploration de l’espace de conception de circuits basés sur les FeFET et FeRAM,

- Les avancées sur la structures des condensateurs TiN/HfZrO2/Ge,

- Le workshop High-k.

Dans le numéro 3 de la newsletter, les 3 parties de ce projets sont mises en avant sont:

- Le travail sur l’interface HfO2/TiN, qui a été publié dans Applied Physics Letters,

- L’intégration de capacités ferroélectriques NZO avec d’excellentes performances,

- La conception de nouvelles cellules logiques basées sur des transistors ferroécletriques

Références et collaborations:

Contact:

Bertrand Vilquin